| Mentor Graphics erweitert Catapult C um Steuerlogik-Support und ermöglicht Highlevel-Synthese von ganzen Chips |

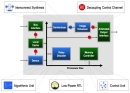

| WILSONVILLE, Oregon/USA, 29. Juni 2009 - Mentor Graphics hat sein Catapult-C-Synthese-Werkzeug um Funktionen zur Unterstützung der Steuerlogik sowie zum Management von Low-Power-Designanforderungen erweitert und ermöglicht nun die Highlevel-Synthese (HLS) von ganzen Chips. Die wegweisende Technologie erlaubt es Designern, sowohl für algorithmische Blöcke als auch für Steuerlogikblöcke reinen ANSI-C++-Code zu verwenden. Die Erweiterung der Catapult-Funktionalität auf die Highlevel-Synthese ganzer Chips ist für den Erfolg eines Designs entscheidend, da Ingenieure aufgrund der schnellen Zunahme der Designgrößen und komplexitäten die Hardwarefunktionalität auf einer höheren Abstraktionsebene entwickeln müssen. Steuerlogiksynthese und algorithmische Synthese wurden traditionell mit Hilfe von verschiedenen Sprachen, Formalismen und Abstraktionen durchgeführt. Die jüngsten Fortschritte im Catapult-C-Synthese-Werkzeug vereinen diese beiden Bereiche und erlauben es dem Anwender, die Steuerlogik zusammen mit dem algorithmischen Verhalten in einem einzigen kohärenten Modell mittels Standard-ANSI-C++ zu beschreiben. Den Kern dieser Innovation bildet ein neues synthetisierbares C++-Konstrukt, mit dem Designer mühelos die asynchrone Datenkommunikation spezifizieren können und dadurch die vollständige Kontrolle über die simultane Hardwareentwicklung erhalten. Dieser zentrale Mechanismus erlaubt die Verbindung von datenflussgesteuerten algorithmischen Darstellungen mit taktsynchronisierten Steuerblöcken. Das Resultat ist eine den Hardwaredesignern vertraute Kodierungsart, mit der sie die Kommunikation, Prioritäten und Aufgabenkoordination innerhalb einer abstrakten Darstellung der Nebenläufigkeit mühelos ausdrücken können. Der neue Ansatz formalisiert eine Modellierungsart, die für steuerungsorientierte Aufgaben nicht nur die erforderliche Genauigkeit bietet, sondern auch die für algorithmische Subsysteme vorteilhafte Abstraktion bewahrt. Der Syntheseprozess wird durch einen zum Patent angemeldeten und vollständig automatisierten Verifikations-Flow ergänzt, mit dem Anwender erstmals detaillierte RTL-Level Block-Interaktionen auf C-Ebene validieren können. Die enge Integration zwischen Verifikation und Synthese untermauert die Notwendigkeit, das volle Potenzial der HLS auszuschöpfen. Ein häufiges Problem bei anderen HLS-Werkzeugen ist die isolierte Entwicklung der Highlevel-Synthese, die zu einer überaus komplexen Verifikation der RTL-Ausgabe führt. Unsere digitalen Broadcasting-ICs bestehen üblicherweise aus einem komplexen Mix von rechenintensiven Einheiten und Steuerblöcken, sagte Professor Michael Schlicht, Gruppenleiter am Fraunhofer-Institut für integrierte Schaltungen. Die neuen Catapult-Erweiterungen zur Steuerlogik-Synthese bieten uns die Funktionen, um einen wachsenden Teil des Gesamtsystems mit Hilfe der Highlevel-Synthese von C++ zu entwickeln. Dies erlaubt es uns, unseren C++-basierten Implementierungs-Flow über die reinen Signalverarbeitungsblöcke hinaus zu erweitern. Zusätzlich zur Unterstützung der Steuerlogik bietet Catapult C Synthesis nun auch für das Low-Power-Design eine wegweisende Technologie, die zwei vorherrschende Designtechniken automatisiert: Clock-Gating auf mehreren Ebenen und die Anbindung an dynamische Power- und Takt-Managementeinheiten. Das Catapult-C-Werkzeug analysiert tiefe Logikkegel, um gateable Takte zu finden. Dies ist eine ansonsten fehleranfällige manuelle Aufgabe, die üblicherweise von Backend-Low-Power-Experten durchgeführt wird. Die neue Optimierung bietet ein beinah 100 Prozent perfektes Clock-Gating, da sie auf Flop-Level arbeitet. Zudem maximiert sie die Leistungseinsparungen durch lokales Erfassen der Gating-Logik, die die Zielregister umgibt. Zur weiteren Leistungsverringerung exportiert das Catapult-C-Synthese-Werkzeug auch Echtzeitinformationen über den Status aller Systemblöcke. Um systemweite Leistungseinsparungen zu erzielen, werden diese Informationen mittels Dynamic Frequency and Voltage Scaling-Heuristik an die Power-Management-Einheiten weitergeleitet. Erwartungsgemäß hängen die dynamischen Leistungseinsparungen vom Design und den Testvektoren ab; Messungen an über 300 Kundendesigns haben Verbesserungen zwischen 10 und 90 Prozent gezeigt, mit einer durchschnittlichen Verbesserung von 40 Prozent. Durch die Steuerlogik-Erweiterungen von Catapult C können wir nun einen größeren Teil unseres Systems mit HLS entwickeln, sagte Emmanuel Liegeon, Deputy-Manager der Digital ASIC & FPGA Design-Group, Thales Alenia Space. Da wir nun mehr und mehr des Systems mit HLS entwickeln, bekommt eine adäquate Leistungsaufnahme ein immer höheres Gewicht. Die neuesten Catapult-C-Erweiterungen für Low-Power bieten die Optimierungen, die wir benötigen. Über Catapult Das Catapult-C-Synthese-Werkzeug ist das erste Produkt zur automatischen Generierung von Steuerlogik- and algorithmischen Multi-Block-Designs auf Registertransferebene aus reinem ANSI-C++-Quellcode, wo sowohl der Kernalgorithmus als auch die Schnittstelle keine Zeitinformationen enthalten. Diese Produktivitätsverbesserung gibt Designern die Zeit und die Freiheit, detaillierte Designanalysen verschiedener Mikroarchitekturoptionen und Schnittstellenszenarien automatisch durchzuführen, um schnell vollständig optimierte Hardwaredesigns zu erlangen. Verfügbarkeit Die neue Version Catapult C Synthesis 2009a ist ab Juli verfügbar. Weitere Informationen gibt es unter: www.mentor.com/products/esl/catapult-c |

| Über Mentor Graphics Mentor Graphics Corporation (Nasdaq: MENT) gehört zu den weltweit führenden Unternehmen, die Software- und Hardwarelösungen für die Entwicklung elektronischer Schaltungen anbieten. Zu Mentors Portfolio gehören Produkte, Beratungs- und Supportdienstleistungen, auf die die weltweit erfolgreichsten Elektronik- und Halbleiterhersteller vertrauen und dies mit der Verleihung zahlreicher Auszeichnungen an Mentor zum Ausdruck gebracht haben. Das 1981 gegründete Unternehmen erzielte in den zurückliegenden zwölf Monaten einen Gesamtumsatz von über 800 Mio. US-Dollar und beschäftigt weltweit ca. 4.500 Mitarbeiter. Der Hauptsitz von Mentor Corporate befindet sich den USA, 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777; Die Adresse der Niederlassung im Silicon Valley lautet: 1001 Ridder Park Drive, San Jose, Kalifornien 95131-2314. Weitere Informationen unter: www.mentor.com Mentor Graphics und Catapult sind eingetragene Warenzeichen der Mentor Graphics Corporation. Alle übrigen Unternehmens- oder Produktnamen sind eingetragene Warenzeichen oder Warenzeichen ihrer jeweiligen Besitzer. |

| Presse Informationen online: | 6166 |

| Presse Informationen | | | Newsletter | | | Suche | | | Agentur | | | English |