| Mentor Graphics präsentiert Calibre RealTime zur sofortigen Signoff-Verifikation von kundenspezifischen IC-Designs |

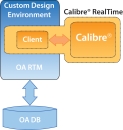

| WILSONVILLE, Oregon/USA, 10. März 2011 - Mentor Graphics kündigt mit Calibre-RealTime eine neue Plattform an, die bereits während der Layouterstellung die physikalische Verifikation in Signoff-Qualität ermöglicht. Die erste Version gestattet die sofortige Prüfung der Entwurfsregeln (Design Rule Checking; DRC) in SpringSofts Laker Custom IC-Design und Layout-Lösungen. Dies geschieht mit den gleichen Calibre-Regeldateien wie im Signoff-Flow. Die neue Lösung beschleunigt den Schaltungsentwurf und verbessert die Qualität der Ergebnisse, da hier den Designern erstmals während der Designphase die volle Leistungsfähigkeit der Calibre-Signoff-Engines in Verbindung mit qualifizierten Regeldateien zur Verfügung steht. Dadurch können sie ihre Layouts hinsichtlich Performance optimieren, ohne Abstriche an der Fertigungsausbeute machen zu müssen. Eine Version für die Mentor Custom IC Designumgebung IC Station wird ab Juni erhältlich sein. Der neue Flow lässt sich nahtlos integrieren und praktisch sofort ausführen, so dass unsere Designer von Foundries qualifizierte Verifikationsinformationen während der Designoptimierung in Echtzeit nutzen können, sagte Richard Rouse, Distinguished-Engineer, MoSys, Inc. Die Implementierung passt ideal in den Designflow. Deshalb ist auch die Einarbeitungsphase sehr kurz. Wegen der Komplexität des physikalischen Designs bei 28 nm waren wir ein wenig besorgt. Weil der Signoff-DRC jedoch unmittelbar während des Layouts zur Verfügung steht und wir uns nicht um die Konsistenz zwischen Design-Tool und Signoff DRC sorgen mussten, wurden viele unserer Bedenken zerstreut. Wir glauben, dass wir mit diesem Flow bei einer typischen Implementierung mindestens eine Woche einsparen können. In den letzten zehn Jahren ist das Handbuch mit Entwurfsregeln für eine neue Technologie von einer dünnen Broschüre mit Dutzenden von Seiten auf einen großen Wälzer mit Hunderten von Seiten angewachsen. Designteams können sich nicht mehr länger auf ihr Gedächtnis und manuelle Prüfungen verlassen, um Verstöße gegen Entwurfsregeln zu vermeiden. Designgruppen, die in 32 nm Technologien und darunter arbeiten, berichten in der Tat über erheblich größere Schwierigkeiten, ein qualitativ hochwertiges, vollständig DRC-sauberes Layout zu erstellen. Dies ist für unsere gemeinsamen Kunden eine interessante neue Möglichkeit, da sie zwei normalerweise verschiedene Aktivitäten Design und Verifikation zusammenbringt, die den Designer noch produktiver machen. Durch den Wegfall von Iterationen, Verzögerungen beim Datentransfer und sich ausbreitende Fehler, die häufig auftreten, wenn die physikalische Verifikation erst spät im Zyklus erfolgt, erhalten Designer Feedback in Signoff-Qualität in Echtzeit und können den gesamten Designzyklus verkürzen, kommentierte JT Li, Vice-President der Physical Design & Technology Product Group von SpringSoft. Um die beste Analogperformance zu erhalten, reizen unsere Designer alle Möglichkeiten der Entwurfsregeln aus, erklärte Ted Buchwald, Senior-Engineer bei Mobius Semiconductor. Nachdem nun während der Layout-Erstellung Signoff-DRCs in Echtzeit zur Verfügung stehen, sind Designer in der Lage, die LVS-DRC-LVS-Schleife zu durchbrechen. Wenn ein Block LVS-sauber ist, ist er auch DRC-sauber und somit bereit zur Extraktion. Dies verändert den Layout-Verifikations-Simulationsflow vollständig und gestattet es, dass wir uns auf das Erreichen der bestmöglichen Ergebnisse konzentrieren. Das Tool wurde unverkennbar von jemandem entwickelt, der persönliche Erfahrung mit Analoglayouts hat. Deshalb scheint es unauffällig im Hintergrund zu bleiben, steht aber immer zur Verfügung, wenn es gebraucht wird und zwar in der Form, in der es der Entwickler tatsächlich benötigt. Wir verbessern kontinuierlich die Laufzeiten aller Produkte innerhalb von Calibre, sagte Joseph Sawicki, Vice-President und General-Manager der Design-to-Silicon-Division von Mentor Graphics. Dadurch, dass Calibre nun auch in der Designerstellungsphase unmittelbar verfügbar ist, können wir die Abweichungen zwischen Design-Tool und Signoff DRC aufheben und Designer produktiver machen. (Mentor Graphics, Mentor, IC Station und Calibre sind eingetragene Warenzeichen der Mentor Graphics Corporation. Alle übrigen Unternehmens- oder Produktnamen sind eingetragene Warenzeichen oder Warenzeichen ihrer jeweiligen Besitzer.) |

| Über Mentor Graphics Mentor Graphics Corporation (Nasdaq: MENT) gehört zu den weltweit führenden Unternehmen, die Software- und Hardwarelösungen für die Entwicklung elektronischer Schaltungen anbieten. Zu Mentors Portfolio gehören Produkte, Beratungs- und Supportdienstleistungen, auf die die weltweit erfolgreichsten Elektronik- und Halbleiterhersteller vertrauen und dies mit der Verleihung zahlreicher Auszeichnungen an Mentor zum Ausdruck gebracht haben. Das 1981 gegründete Unternehmen erzielte in den zurückliegenden zwölf Monaten einen Gesamtumsatz von über 800 Mio. US-Dollar. Der Hauptsitz von Mentor Corporate befindet sich den USA, 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777. Weitere Informationen unter: www.mentor.com |

| Presse Informationen online: | 6166 |

| Presse Informationen | | | Newsletter | | | Suche | | | Agentur | | | English |