| Mentor Graphics Introduces Calibre RealTime for Instant Signoff Verification of Custom IC Designs |

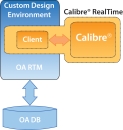

| WILSONVILLE, Ore., March 10, 2011 - Mentor Graphics Corporation (NASDAQ: MENT) today announced the new Calibre® RealTime platform for signoff-quality physical verification during design creation. The first release provides instantaneous design rule checking (DRC) in the SpringSoft Laker custom IC design and layout solution, using the same Calibre decks as the signoff flow. The new solution improves design speed and quality of results by giving designers, for the first time, the full power of Calibres signoff engines and qualified decks during design. This allows them to optimize their layouts for performance without sacrificing manufacturing yield. A version for the Mentor® IC Station® custom design environment will be available in June. The new flow is seamless and virtually instantaneous, allowing our designers to use foundry-qualified verification information during design optimization in real time, said Richard Rouse, Distinguished Engineer at MoSys, Inc. The implementation fits naturally into the design flow so the learning curve is very fast. We were a bit concerned about the complexity of physical design at 28nm, but having the signoff DRC instantaneously available during layout, and not having to worry about consistency between the design tool DRC and signoff, has removed a lot of our concerns. We believe that we can save at least a week on a typical implementation project with this flow. Over the last 10 years, the design rule manual for a new technology has grown from a small pamphlet of dozens of pages into a grand tome with hundreds of pages. Design teams can no longer rely on their memory and manual checks to avoid design rule violations in their layouts. Design groups working at 32nm and beyond are in fact reporting a significant increase in the difficulty of converging to a high-quality layout that is completely DRC-clean. This is an exciting new capability for our mutual customers because it brings what used to be two different activities -design and verification together to make the designer more productive. By eliminating iterations, data transfer delays, and ripple effects that are common when physical verification is left until later in the cycle, designers can get sign-off quality feedback in real time and shorten the overall design cycle, said JT Li, VP of Physical Design & Technology Product Group at SpringSoft. Our designers are pushing the limits of the design rules to get the best analog performance, said Ted Buchwald, a senior engineer at Mobius Semiconductor. "Having the signoff design rule checks in real time, while creating the layout, allows the designer to break the LVS-DRC-LVS loop. When a block is LVS-clean, it's DRC-clean and ready for extraction. It completely changes the layout-verification-simulation flow and lets us focus on getting the best results possible. The tool was clearly designed by someone with first-hand analog layout experience. in that it never seems to be in the way, but yet is always available to be used when and how the designer wants to use it." We are continuously improving the run times for all the products within the Calibre offering, said Joseph Sawicki, vice president and general manager of the Design-to-Silicon division of Mentor Graphics. By making Calibre also instantly available in the design creation phase, we can short-circuit the divergence between design tool checking and signoff and make custom designers more productive. (Mentor Graphics, Mentor, IC Station, and Calibre are registered trademarks of Mentor Graphics Corporation. All other company or product names are the registered trademarks or trademarks of their respective owners.) |

| About Mentor Graphics Mentor Graphics Corporation (NASDAQ: MENT) is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the worlds most successful electronics and semiconductor companies. Established in 1981, the company reported revenues over the last 12 months of about $800 million. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777. World Wide Web site: http://www.mentor.com |

| Presse Informationen online: | 6571 |

| Presse Informationen | | | Newsletter | | | Suche | | | Agentur | | | English |